转自homg.es

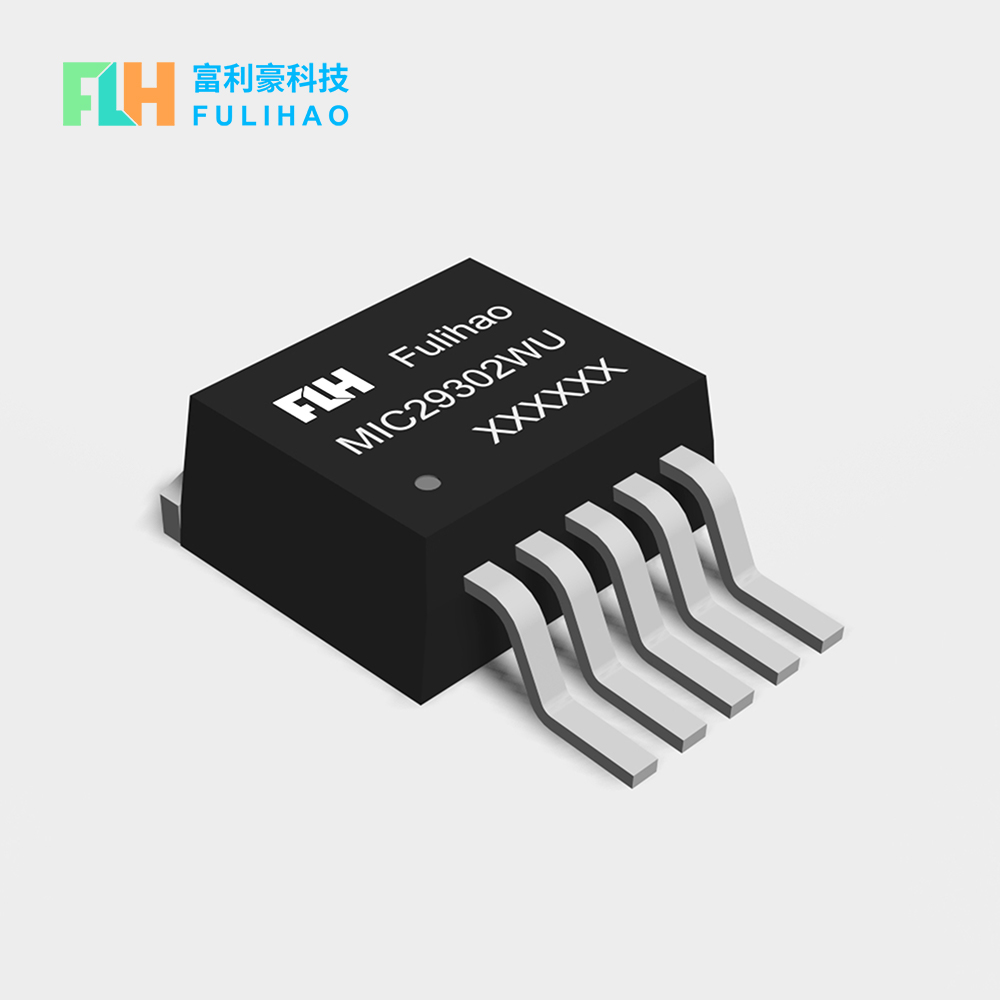

A small outline integrated circuit (SOIC) is a surface-mounted integrated circuit (IC) package which occupies an area about 30–50% less than an equivalent dual in-line package (DIP), with a typical thickness being 70% less. They are generally available in the same pin-outs as their counterpart DIP ICs. The convention for naming the package is SOIC or SO followed by the number of pins. For example, a 14-pin 4011 would be housed in an SOIC-14 or SO-14 package.

JEDEC and JEITA/EIAJ standards

Small outline actually refers to IC packaging standards from at least two different organizations:

- JEDEC:

- JEITA (previously EIAJ, which term some vendors still use):

- Semiconductor Device Packages. (EIAJ Type II is 5.3 mm body width, and slightly thicker and longer than JEDEC MS-012.)

Note that because of this, SOIC is not specific enough of a term to describe parts which are interchangeable. Many electronic retailers will list parts in either package as SOIC whether they are referring to the JEDEC or JEITA/EIAJ standards. The wider JEITA/EIAJ packages are more common with higher pin count ICs, but there is no guarantee that an SOIC package with any number of pins will be either one or the other.

However, at least Texas Instruments[1] and Fairchild Semiconductor consistently refer to JEDEC 3.9 and 7.5 mm width parts as “SOIC” and to EIAJ Type II 5.3 mm width parts as “SOP”.

General package characteristics

The SOIC package is shorter and narrower than DIP, the side-to-side pitch being 6 mm for an SOIC-14 (from lead tip to lead tip), and the body width being 3.9 mm. These dimensions differ depending on the SOIC in question, and there are several variants. This package has “gull wing” leads protruding from the two long sides and a lead spacing of 0.050 in (1.27 mm).

SOIC (JEDEC)

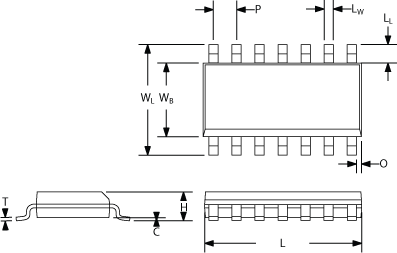

The picture below shows the general shape of a SOIC narrow package, with major dimensions. The values of these dimensions (in millimetres) for common SOICs is shown in the table.

| C | Clearance between IC body and PCB |

| H | Total carrier height |

| T | Lead thickness |

| L | Total carrier length |

| LW | Lead width |

| LL | Lead length |

| P | Pitch |

| WB | IC body width |

| WL | Lead-to-lead width |

| O | End overhang |

| Package | WB | WL | H | C | L | P | LL | T | LW | O |

|---|---|---|---|---|---|---|---|---|---|---|

| SOIC-8-N | 3.8–4.0 | 5.8–6.2 | 1.35–1.75 | 0.10–0.25 | 4.8–5.0 | 1.27 | 0.41 (1.04) | 0.19–0.25 | 0.35–0.51 | 0.33 |

| SOIC-14-N | 3.8–4.0 | 5.8–6.2 | 1.35–1.75 | 0.10–0.25 | 8.55–8.75 | 1.27 | 1.05 | 0.19–0.25 | 0.39–0.46 | 0.3–0.7 |

| SOIC-16-N | 3.8–4.0 | 5.8–6.2 | 1.35–1.75 | 0.10–0.25 | 9.8–10.0 | 1.27 | 1.05 | 0.19–0.25 | 0.39–0.46 | 0.3– 0.7 |

SOP (JEITA/EIAJ)

These are sometimes called “wide SOIC”, as opposed to the narrower JEDEC MS-012, but they in turn are narrower than the JEDEC MS-013, which may also be called “wide SOIC”.

| Package | WB | WL |

|---|---|---|

| SOIC-8 | 5.41 (5.16) | 8.07 (7.67) |

Next to the narrow SOIC package (commonly represented as SOx_N or SOICx_N, where x is the number of pins), there’s also the wide (or sometimes called extended) version. This package is commonly represented as SOx_W or SOICx_W.

The difference is mainly related to the parameters WB and WL. As an example, the values WB and WL are given for an 8-pins wide (extended) SOIC package.

mini-SOIC

| Package | WB | WL | H | C | L | P | LL | T | LW |

|---|---|---|---|---|---|---|---|---|---|

| miniSOIC-10 | 3.0 | 4.9 | 1.09 | 0.10 | 3.0 | 0.5 | 0.95 | 0.19 | 0.23 |

Another SOIC variant, available only for 8-pin and 10-pin ICs, is the mini-SOIC, also called micro-SOIC. This case is much smaller, with a pitch of only 0.5 mm. See the table for the 10-pin model.

An excellent overview of different semiconductor packages is provided by National Semiconductor.[2]

Small-outline J-leaded package (SOJ)

Small-outline J-leaded package (SOJ) is a version of SOIC with J-type leads instead of gull-wing leads.[3]

Smaller form factors

After SOIC came a family of smaller form factors with pin spacings less than 1.27 mm:

- Thin small outline package (TSOP)

- Thin-shrink small outline package (TSSOP)

Shrink small-outline package (SSOP)

Shrink small-outline package (SSOP) chips have “gull wing” leads protruding from the two long sides, and a lead spacing of 0.0256 inches (0.65 mm) or 0.025 inches (0.635 mm).[4] 0.5 mm lead spacing is less common, but not rare.

The body size of a SOP was compressed and the lead pitch tightened to obtain a smaller version SOP. This yields an IC package with a significant reduction in the size compared to standard package. All IC assembly processes remain the same as with standard SOPs.

Applications for a SSOP enable end-products (pagers, portable audio/video, disc drives, radio, RF devices/components, telecom) to be reduced in size and mass. Semiconductor families such as operational amplifiers, drivers, optoelectronics, controllers, logic, analog, memory, comparators and more using BiCMOS, CMOS or other silicon / GaAs technologies are well addressed by the SSOP product family.

Thin small-outline package (TSOP)

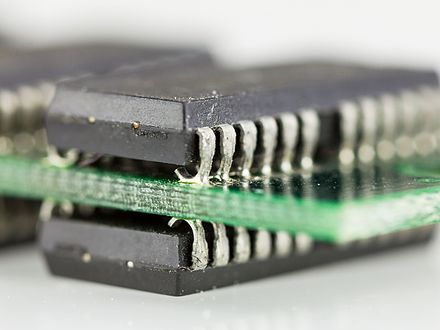

A thin small-outline package (TSOP) is a rectangular, thin-bodied component. A Type I TSOP has legs protruding from the width portion of the package. A Type II TSOP has the legs protruding from the length portion of the package. The ICs on DRAM memory modules were usually TSOPs until they were replaced by ball grid array (BGA).

Thin-shrink small-outline package (TSSOP)

A thin-shrink small-outline package (TSSOP) is a rectangular, thin-body component. A TSSOP’s leg count can range from 8 to 64.

TSSOPs are particularly suited for gate drivers, controllers, wireless / RF, op-amps, logic, analog, ASICs, memory (EPROM, E2PROM), comparators and optoelectronics. Memory modules, disk drives, recordable optical disks, telephone handsets, speed dialers, video / audio and consumer electronics / appliances are suggested uses for TSSOP packaging.

Exposed pad

The exposed pad (EP) variant of small outline packages can increase heat dissipation by as much as 1.5 times over a standard TSSOP,[citation needed] thereby expanding the margin of operating parameters. Additionally, the exposed pad can be connected to ground, thereby reducing loop inductance for high-frequency applications. The exposed pad should be soldered directly to the PCB to realize the thermal and electrical benefits.

References

- ^ “TI Small Outline Packages”. Texas Instruments. Retrieved 2020-06-02.

- ^ National Semiconductor Selection Guide by Package Products, National.com, archived from the original on 2012-04-27, retrieved 2012-04-27

- ^ “IC Package Types”. Archived from the original on 2011-07-16. Retrieved 2013-01-01.

- ^ “Package Dimensions: MSOP8/-TP, SSOP20/28, TSSOP16, TSSOP20/-TP, TSSOP24” (PDF). IC Haus. Retrieved 23 September 2018.

External links

- Amkor Technology SOIC Package

- Amkor Technology ExposedPad SOIC/SSOP Package

- Amkor Technology SSOP package.

- Image of a 74HC4067 multiplexer chip in a SSOP package. A US quarter is shown for a size reference.